## Logic Synthesis and Optimization of Reversible and Quantum Circuits for Arithmetic Logic Units

Md Belayet Ali

Department of Electrical Engineering and Computer Science Graduate School of Engineering

Iwate University

A thesis submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

March 2019

## Dedication

.

To my parents, who taught me the most important values in life.

## ACKNOWLEDGEMENT

First and foremost, I would like to thank my advisor Takashi Hirayama from the Department of Electrical Engineering and Computer Science, Faculty of Engineering, Iwate University, Japan. It has been an honor to be his first Ph.D. student. I appreciate all his contributions, especially his time and ideas, to make my Ph.D. experience productive and stimulating. The joy and enthusiasm he has for his research were contagious and motivated me during tough times in the pursuit of the degree. I am also thankful to him for serving as an excellent example, both as a successful supervisor and human being.

I would also like to thank Yasuaki Nishitani, retired Professor of the Department of Electrical Engineering and Computer Science, Faculty of Engineering, Iwate University, Japan, for his valuable discussions, comments, and encouragements in this research.

I would also like to thank Katsuhisa Yamanaka, Assistant Professor of the Department of Electrical Engineering and Computer Science, Faculty of Engineering, Iwate University, Japan, for being part of my thesis committee, for his support, and for being an inspiration in many ways.

I would also like to thank the members of the Hirayama-Yamanaka (former Nishitani-Hirayama) laboratory contributing to my personal and professional time at Iwate University. They have been a source of friendships as well as good advice and collaboration. I am especially grateful to the following members of the former Nishitani-Hirayama laboratory who stuck with me during my Master's course: Tadayoshi Miura, Takafumi Omori, Yoji Sato, Kota Abe, and Gaku Yasui. I would like to especially acknowledge Miura-san and his parents; he was my Master's classmate, lab mate, and tutor. I would also like to thank the following past and present lab members that I have had the pleasure to work with: graduate students Hayato Sugawara, Masatoshi Murakami, Hiroki Kaga, Rin Suzuki, Akihiro Yokota, Takafumi Maki, and Koki Kainuma; undergraduate students Koki Takahashi, Toshiki Matsuno, Seunghun Shin, and Dai Ito; and the numerous 3rd and 4th (grade) students who have come through the lab.

I grateful to several funding sources that made my Ph.D. work possible. I was funded by the Ministry of Education, Culture, Sports, Science, and Technology, also known as MEXT, Monkasho, and formerly the Ministry of Education, Science, and Culture, which is a ministry of the Japanese government who supported my initial six months as a research student, two years as a Master's student, and three years as a Ph.D. student. I was also supported by the Faculty of Engineering, Iwate University.

My time at Morioka, Iwate was made enjoyable in large part due to my wife, my dearest son, and many friends and groups that have become a part of my life. I am grateful for the time spent with my wife Nishat Tasmin, and also with my son Mohammad Yusuf Ibn Ali, and for preparing delicious meals, for the memorable trips to Miyako city and Mount. Fuji, and for her great support as I finished up my degree. My time at Morioka, Iwate was also enriched by the International Students Association, Morioka Cricket Club, and the International Students Soccer team.

I would like to thank my family for all their love and encouragement. First, to • my parents who raised and supported me in all my pursuits. And most of all to my loving, supportive, encouraging, and patient wife Nishat, whose faithful support during the final stages of the Ph.D. is very much appreciated. Thank you.

Finally, I thank the Almighty Lord for keeping me in good health and spirits throughout my research work.

March 2019 Md Belayet Alia

## Abstract

Reversible computing is generally considered to be an unconventional form of computing, which has drawn considerable attention from researchers in order to design low-power computing devices. Furthermore, reversible logic plays an important role in the field of quantum computation. However, the synthesis of reversible logic for building quantum circuits is notably dissimilar from the synthesis of non-reversible logic. In the process of reversible logic synthesis, the design of reversible functions is very important and the embedding of irreversible functions into reversible functions is required before they can be applied to existing synthesis methods.

In this thesis, we focus on logic synthesis and optimization of reversible and quantum circuits for arithmetic logic units (ALUs). The main concept of our approach is different from those of existing related studies; in particular, we put emphasis on function design. ALU is a key element for any programmable computing device. In the design of ALUs, an adder/subtractor block is another important key element. A faster adder/subtractor block help improve the efficiency of the ALUs performance and that of the whole system. In this thesis, we propose a design of reversible adder/subtractor blocks and ALUs. Our approach to investigate the reversible functions includes (a) the embedding of irreversible functions into incompletely-specified reversible functions, (b) the operation assignment (OA), and (c) the permutation of function outputs. Moreover, we provide some extensions of these techniques to further improve the design of reversible functions.

We propose a minimization algorithm to obtain minimum multiple-control Toffoli (MCT) circuits. The algorithm comprises the OA and the permutation of function outputs to reduce the number of gates in a circuit. We use hash tables of minimum MCT circuits, which are simply constructed using an exhaustive enumeration of gate combinations. The resulting reversible circuits are smaller than existing designs in terms of the number of MCT gates. To evaluate the quality of the reversible circuits, we also propose a greedy algorithm and obtain reduced quantum circuits. The results demonstrate the superiority of our realization of adder/subtractor blocks and ALUs with respect to quantum cost.

۰.

1. A.

## Contents

| D  | EDIC  | CATION                                      | 3  |

|----|-------|---------------------------------------------|----|

| A  | CKN   | OWLEDGEMENT                                 | 5  |

| Al | ostra | $\mathbf{ct}$                               | 7  |

| 1  | Intr  | oduction                                    | 1  |

|    | 1.1   | Introduction                                | 1  |

| 2  | Basi  | ic Definitions                              | 7  |

|    | 2.1   | Boolean Logic Functions                     | 7  |

|    | 2.2   | Reversible Logic Functions                  | 8  |

|    | 2.3   | Reversible Gates                            | 9  |

|    | 2.4   | Reversible Circuits                         | 10 |

|    | 2.5   | Quantum Computation                         | 10 |

|    | 2.6   | Quantum Gates                               | 11 |

|    | 2.7   | Quantum Circuits                            | 14 |

| 3  | Lite  | rature Review                               | 17 |

|    | 3.1   | Related Works                               | 17 |

| 4  | Des   | ign of Reversible Functions                 | 19 |

|    | 4.1   | Embedding Irreversible Functions into       |    |

|    |       | Incompletely-Specified Reversible Functions | 19 |

|    | 4.2   | Operation Assignment (OA)                   | 21 |

|    | 4.3   | Permutation of Function Outputs             | 23 |

| 5  | Syn   | thesis of Minimum Reversible Circuits       | 25 |

|    | 5.1   | Minimization Algorithm                      | 25 |

|    | 5.2   | Reversible Adder/Subtractor                 | 26 |

| •      |    | 5.2.1 Half Adder/Subtractor                                    | 26 |

|--------|----|----------------------------------------------------------------|----|

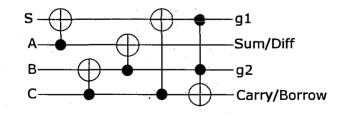

|        |    | 5.2.2 Full Adder/Subtractor                                    | 30 |

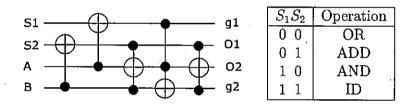

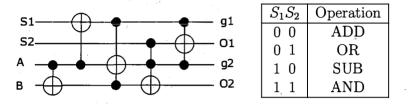

|        |    | 5.3 Simple Reversible Arithmetic Logic Units (ALUs)            | 33 |

| •      |    | 5.3.1 1-bit Arithmetic Logic Unit (ALU) Benchmarks             | 34 |

| • •    |    | 5.3.2 Revised Arithmetic Logic Units (ALUs)                    | 34 |

|        |    | 5.4 Experimental Results                                       | 35 |

|        | 6  | Quantum Circuit Synthesis                                      | 41 |

|        |    | 6.1 Reduction of Quantum Costs (QCs)                           | 42 |

| ÷      | ·  | 6.2 Comparison of Quantum Costs (QCs)                          | 44 |

| •      |    | 6.3 Experimental Results                                       | 45 |

| •<br>• | 7  | Conclusions and Future Works                                   | 49 |

|        | Α  | Truth Table Representation of Reversible Arithmetic Logic Unit | S  |

|        |    | (ALUs)                                                         | 53 |

| •      | Bi | bliography                                                     | 57 |

# List of Figures

| 1.1 | Overview of the design flow of reversible synthesis                       | 2    |

|-----|---------------------------------------------------------------------------|------|

| 2.1 | MCT gate library: (a) NOT, (b) CNOT, and (c) Toffoli.                     | 9    |

| 2.2 | Reversible circuit.                                                       | 10   |

| 2.3 | Splitting and merging rules                                               | • 12 |

| 2.4 | Deletion rule.                                                            | 12   |

| 2.5 | Merged 2-qubit gate.                                                      | 13   |

| 2.6 | Quantum gate representation of the Fredkin Gate                           | 14   |

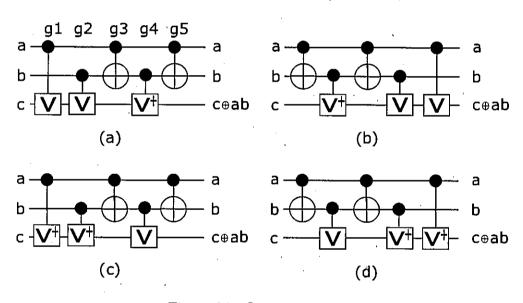

| 2.7 | Quantum circuit.                                                          | 15   |

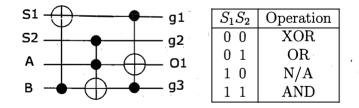

| 4.1 | (a) Circuit realizing ALU. (b) Circuit realizing OAEC(ALU).               | 23   |

| 4.2 | Circuit realizing $PEC(ALU)$                                              | 24   |

| 5.1 | Simple minimization algorithm with up to $m$ gates $\ldots \ldots \ldots$ | . 27 |

| 5.2 | Proposed reversible half adder/subtractor circuit with MCT gates          | 29   |

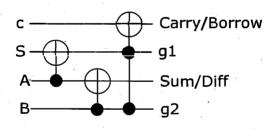

| 5.3 | Proposed reversible full adder/subtractor circuit with MCT gates. $\ .$ . | 31   |

| 5.4 | Mini-ALU: Minimum MCT circuit and its OA.                                 | 34   |

| 5.5 | Gupta's-LU: Minimum MCT circuit and its OA.                               | 34   |

| 5.6 | ALU: Minimum MCT circuit and its OA.                                      | 35   |

| 5.7 | LU: Minimum MCT circuit and its OA                                        | 35   |

| 6.1 | Simple algorithm to obtain reduced quantum circuits.                      | 42   |

| 6.2 | Reduced half adder/subtractor circuit with quantum gates.                 | 43   |

| 6.3 | Reduced full adder/subtractor circuit with quantum gates                  | 43   |

| 6.4 | Reduced ALU circuit with quantum gates                                    | 43   |

## List of Tables

| 2.1  | Truth table of a 2-input OR gate                                         | 7  |

|------|--------------------------------------------------------------------------|----|

| 2.2  | Truth table of a NOT gate                                                | 8  |

| 2.3  | Classical reversible function                                            | 8  |

| 2.4  | Quantum gate symbols and unitary matrices [1]                            | 11 |

| 3.1  | Comparison of existing reversible adder/subtractor circuits              | 18 |

| 3.2  | Related works on reversible ALUs.                                        | 18 |

| 4.1  | Incompletely-specified function ALU.                                     | 21 |

| 4.2  | Four operations of ALU.                                                  | 22 |

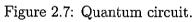

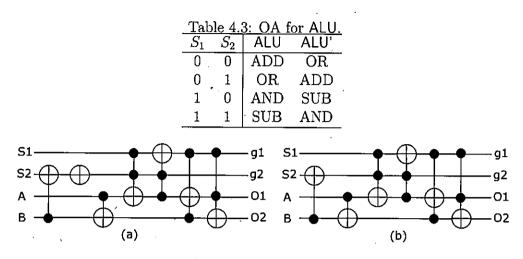

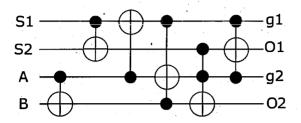

| 4.3  | OA for ALU                                                               | 23 |

| 5.1  | OA for adder/subtractor                                                  | 26 |

| 5.2  | Incompletely specified half adder/subtractor function $hAS_1$            | 28 |

| 5.3  | Incompletely specified half adder/subtractor function $hAS_2.$           | 28 |

| 5.4  | $OPT(PEC(hAS_1))$ and its minimum MCT circuits $\ldots \ldots \ldots$    | 29 |

| 5.5  | $OPT(PEC(hAS_2))$ and its minimum MCT circuits $\ldots \ldots \ldots$    | 29 |

| 5.6  | Incompletely specified full adder/subtractor function $fAS_1.\ \ldots$ . | 30 |

| 5.7  | Incompletely specified full adder/subtractor function $fAS_2.$           | 31 |

| 5.8  | $OPT(PEC(fAS_1))$ and its minimum MCT circuits.                          | 32 |

| 5.9  | $OPT(PEC(fAS_2))$ and its minimum MCT circuits                           | 33 |

| 5.10 | Computer specifications.                                                 | 36 |

| 5.11 | Summary of all generated reversible functions for adder/subtractors      | 36 |

| 5.12 | Computation time [second] of experiments in Table 5.11.                  | 36 |

| 5.13 | Comparison of the proposed reversible full adder/subtractor and exist-   |    |

|      | ing counterparts.                                                        | 37 |

| 5.14 | OPT(PEC(OAEC(F)))  of 1-bit ALUs and computation time                    | 38 |

| 5.15 | Comparison of 1-bit ALUs                                                 | 39 |

| 6.1  | Computer specifications.                                                 | 45 |

| 6.2 | Reduction of QC in the half adder/subtractor $hAS_1$                    | 45  |

|-----|-------------------------------------------------------------------------|-----|

| 6.3 | Reduction of QC in the full adder/subtractor $fAS_1$ .                  | 46  |

| 6.4 | OPT(PEC(F))  of adder/subtractor and computation time for QC reduction. | 46  |

| 6.5 | Comparison of the proposed reversible full adder/subtractor and exist-  | · . |

|     | ing counterparts.                                                       | 47  |

| 6.6 | Comparison of 1-bit ALUs                                                | 47  |

| A.1 | Truth table representation of reversible LU                             | 54  |

| A.2 | Truth table representation of reversible ALU                            | 54  |

| A.3 | Truth table representation of Gupta's-LU                                | 55  |

| A.4 | Truth table representation of Mini-ALU                                  | 56  |

vi

# Chapter 1 Introduction

#### 1.1 Introduction

In the modern age of science and technology, the world of computing is in a transition period. As chips become smaller and faster, the amount of dissipated heat, which is the energy that is entirely wasted, is increasing. According to Rolf Landauer's principle, the thermodynamic cost of a bit of information acquisition or destruction is, at least,  $kT \ln 2$  [Joule], where k is the Boltzmann's constant and T is the temperature [2]; at room temperature, the amount of dissipated heat per bit is small (i.e.,  $2.9 \times 10^{-21}$  [Joule]). According to Moore's Law, the advancement of technologies is achieved by the exponential downscaling of transistors and the doubling of the number of transistors per area unit every 18 months [3]. However, reducing the transistor's size and placing a high volume of transistors on a chip can lead to severe problems related to stable computing in nanoscale devices.

Logic synthesis is the process of realizing logic functions in terms of primitives (gates). In today's computers, whenever a logical operation is performed part of the information is erased. Logic operations in computing devices with conventional technology are performed using the logic gates AND, OR, and NOT. The AND and OR gates are irreversible in the sense that they destroy information as they give a single output for multiple inputs. To recover the destroyed information, additional computation is needed, which means the system will eventually dissipate heat to generate the destroyed information. Hence, it is essential to find more efficient forms of computation or alternative forms of computation to overcome such problems. One of the outside runners in the race to take the world of logic by storm is reversible computing. Reversible computing is the path to future computing technologies, which all happen to use reversible logic.

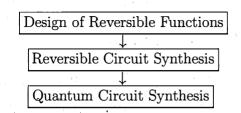

Figure 1.1: Overview of the design flow of reversible synthesis

Synthesis of reversible logic has been an active research area. Reversible logic has the same number of inputs and outputs with a one-to-one mapping between vectors of inputs and outputs; thus, the vector of input states can always be reconstructed from the vector of output states. Consequently, a computation is reversible if it is always possible to uniquely recover the input for a given output. Designs with information loss are not logically reversible [2]. Bennet [4] showed that reversible computation can be potentially performed without losing energy. Systems that are not reversible can be transformed into reversible systems by storing all the input information. This promising approach reduces energy loss. However, many computational problems, such as integer factoring, are exponentially hard to solve.

Recently, several studies have investigated reversible circuit synthesis [5, 6, 7, 8]. Figure 1.1 shows an overview of the design flow of reversible synthesis. The primary goal of designing cost-efficient reversible circuits is to minimize the cost of the circuits in terms of a few metrics such as the number of constant inputs, garbage outputs [9, 10], reversible gates [11], and quantum cost (QC) [12, 13, 14, 15]. Constant inputs are lines that exist on the input side with a certain fixed logical value, either 0 or 1, whereas garbage outputs exist on the output side and do not perform any useful operation to facilitate further computations. Both constant inputs and garbage outputs are simply added to the circuit at the design stage of reversible functions to maintain reversibility.

From published studies, it was observed that multiple-control Toffoli (MCT) gates can be extensively used to synthesize a reversible circuit [16, 17, 18]. Therefore, the number of MCT gates is generally used as the cost metric during the stage of reversible circuit synthesis. A reversible circuit is further decomposed into cascades of elementary quantum gates [19, 20, 21], which is called a quantum circuit. Recently, much attention has been given to the synthesis of quantum circuits because of the potential to exponentially speed-up quantum computation. At the stage of the quantum circuit synthesis, the QC is the most common cost metric, which is measured by counting the number of elementary quantum gates required to implement the quantum circuit. The fundamental unit of information in quantum computation is the qubit. The computational basis states of a qubit are analogous to the states of a bit in classical computation [22]. According to the principles of quantum mechanics, the logic operation of quantum systems is entirely different from its classical counterpart [22]. The qubit can be described by a state vector in a two-dimensional complex vector space. An infinite state space can be found in this computation by superposition of states [22]. The transition between states of a quantum system is described by a unitary transformation. Unitary operations are reversible and no information is lost in the process. In building a general-purpose quantum computer, it is important to embed Boolean logic functions into quantum gates and devices.

Quantum gates are represented by unitary matrices, which may include complex elements [22], and many sets of gates are universal. The most commonly used quantum gate library includes Toffoli and NCV (NOT, CNOT, Controlled-V, and Controlled- $V^{\dagger}$  gates). The underlying methods for synthesis include embedding irreversible functions into reversible functions, realizing reversible circuits from reversible functions, and mapping reversible circuits into quantum circuits. Reversible functions are a special case of multiple output Boolean logic functions and can be realized by quantum circuits by cascading quantum gates. The cost factors for quantum circuits are the number of elementary quantum gates used and the number of qubits. Moreover, the QC is the most prevalent criteria to measure the quality of circuits. The resulting decomposed quantum circuits can be further optimized in order to reduce the QC.

The most promising application of reversible logic is quantum computation. Quantum operations are all reversible, and every classical reversible circuit may be implemented in quantum technology. Researchers have used quantum computation to solve many practically relevant problems faster than traditional computing machines. For example, the factorization problem in polynomial time can be solved by quantum computation, whereas, only exponential algorithms are known for traditional machines. Even though research in this area is still on its early stages, promising applications to future computing devices motivate further research.

Reversible computing is considered as an unconventional form of computing, but it has recently drawn considerable attention from researchers in order to design lowpower computing devices. The arithmetic logic unit (ALU) is a key element for any programmable computing devices. In the design of ALUs, an adder/subtractor block is an important key element. A faster adder/subtractor block helps improve the efficiency of the ALUs performance and that of the whole system. In this thesis, we focus on logic synthesis and optimization of reversible and quantum circuits for ALUs by putting emphasis on the function design, which makes our approach different from those of existing related studies. Our approach to investigate reversible functions includes (a) the embedding of irreversible functions into incompletely-specified reversible functions, (b) the operation assignment (OA), and (c) the permutation of function outputs. We also give some extensions of these techniques to further improve the design of reversible functions. The objective of this research is to design ALUs or adder/subtractor blocks that have better performance and lower power consumption than existing systems. Therefore, it is important to have fast reversible ALUs and adder/subtractor blocks because their performance could affect the efficiency of the whole system.

Over the last decades, Toffoli, Peres, and Fredkin are conventionally used to synthesize reversible circuits. Here, we adopt the MCT gate library to design reversible adder/subtractor and simple ALU circuits. As far as we know, there are no existing works on the optimization of reversible full adder/subtractor circuits using only the MCT gate library with the lowest possible number of working lines, constant inputs, and garbage outputs though the MCT gate library is the most fundamental and widely-used gate library for the synthesis of reversible circuits. The major contributions of this work are as follows:

- Embedding of irreversible functions into incompletely-specified reversible functions. The functions of the adder/subtractor and ALU are irreversible. To obtain a reversible circuit of an irreversible function, we embed the irreversible function into an incompletely-specified function to make it reversible. We set a restriction in which only the minimum necessary ancilla lines are added for embedding. Ancilla lines refer to when additional input Boolean variables are needed to construct the output function. Minimization of the number of reversible gates, ancilla lines, and garbage outputs is one of the major goals in reversible logic design and synthesis.

- 2. The operation assignment: This is the unique and interesting point is our idea of improvement of reversible circuits. We introduce a new approach called synthesis with OA. It is a permutation of groups of rows in a truth table. Even if the set of operations is the same, the functions consisting of the operations vary according to the assignment of the operations. Our approach is to try all permutations of operations and find the minimum circuit realization.

- 3. Permutation of function outputs. The idea of permutation of outputs of a reversible function was originally introduced by Wille et al. [23], called as Synthesis with Output Permutation (SWOP). SWOP can be easily applied by encoding all output permutations, synthesizing each in one turn, and keeping the best one.

- 4. Minimization algorithm. We propose a minimization algorithm to obtain the minimum MCT circuits. It consists of the OA and the permutation of function outputs to further reduce the number of gates in a circuit. We use the hash tables of minimum MCT circuits with up to seven gates for 4-bit functions and five gates for 5-bit functions. The tables are constructed by enumerating all possible gate combinations.

- 5. Quantum circuit synthesis. We obtain quantum circuits of our reversible adder/subtractors and ALUs by applying a greedy algorithm. The algorithm performs the transformation of a given MCT circuit into a quantum circuit, searches a pair of adjacent gates in the circuit by moving the gate according to the moving rule, and applying different rules to obtain the reduced quantum circuit. The execution of moving and reducing gate is repeated if the quantum gates in the quantum circuit are reduced successively.

This thesis is organized as follows.

- In Chapter 2, we outline some preliminaries of reversible and quantum circuits. We also defineirreversible and reversible logic functions. The fundamentals of quantum computation will help readers to understand logic representations in quantum computations.

- In Chapter 3, we analyze and identify problems of previous synthesis and optimization approaches.

- In Chapter 4, we propose design techniques specific to reversible functions of adder/subtractor blocks and ALUs.

- In Chapter 5, we discuss the proposed minimization algorithm for MCT circuits and obtain the minimum MCT circuits of adder/subtractor and ALUs. We also discuss the experimental results of minimum MCT circuits as compared with existing counterparts.

• In Chapter 6, we describe the transformation of MCT circuits into quantum circuits with the NCV gate library and the reduction of the quantum circuits with a simple greedy algorithm. We also show how the experimental results demonstrate the superiority of our realization of adder/subtractor blocks and ALUs with respect to the QC.

• In Chapter 7, we summarize our contributions, culminating with suggestions for future works.

6

### Chapter 2

## **Basic Definitions**

This chapter provides basic definitions and notations to keep this thesis self-contained. In this chapter, some important factors of Boolean logic functions, reversible computing, and quantum computation are explained.

#### 2.1 Boolean Logic Functions

A logic function can be a top-level design entity, which is a logic function that is the root of a design hierarchy, or a lower-level logic function. In binary relation from the set A to B, a function is denoted by

$f: A \to B$ ,

where for each element  $a \in A$  there exists a unique element  $b \in B$ . The relation may be many-to-one or one-to-one. A k-input Boolean logic function

$f: B^k \to B,$

defined over the set  $B = \{0, 1\}$ , represents certain propositions whose results would either be 1 (true) or 0 (false).

| Input | Output |

|-------|--------|

| 00    | 0      |

| 01    | 1      |

| 10    | , 1    |

| 11    | 1      |

Table 2.1: Truth table of a 2-input OR gate

Logic synthesis is the process of realizing logic functions in terms of primitives (gates). Logic operations in computing devices with conventional technology are

#### Table 2.2: Truth table of a NOT gate

|   | Input | Output |

|---|-------|--------|

| , | • • 0 | 1      |

|   | 1     | 0      |

performed by using the logic gates AND, OR, and NOT. Table 2.1 shows the logic function of a 2-input OR gate. The AND and OR gates are not reversible because they destroy information whenever as they provide a single output for two inputs. On the other hand, the logic function of the NOT gate has a one-to-one correspondence between input and output. That is, no information is lost in the logic operation of the NOT gate, and hence, it is reversible. An example of a reversible function is shown in Table 2.2.

#### 2.2 Reversible Logic Functions

The main object in reversible logic theory is the reversible function, defined as follows [5, 9].

**Definition 1** The function  $f(x_1, x_2, ..., x_n)$  of n Boolean variables is called reversible if:

1. the number of outputs is equal to the number of inputs.

2. any input pattern maps to a unique output pattern.

In the literature, reversible functions are also referred to as classical reversible functions [22]. Table 2.3 shows a classical reversible function.

| ). | Classic | al reversit | 11 |

|----|---------|-------------|----|

|    | Input   | Output      |    |

|    | 00      | . 00        |    |

|    | 01      | :01         |    |

|    | 10      | 11          |    |

|    | 11      | 10          |    |

|    |         |             |    |

Table 2.3: Classical reversible function

In other words, the output of a reversible function is a permutation of the set of its input [5], [24]. For an (n, k) function, i.e., a function with *n*-inputs *k*-outputs, it is necessary to add inputs and/or outputs to make it reversible. This leads to the following definition.

8

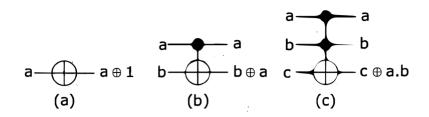

Figure 2.1: MCT gate library: (a) NOT, (b) CNOT, and (c) Toffoli.

**Definition 2** "Garbage" is the number of outputs added to make an (n, k) function reversible. While the word "constant inputs" is used to denote the preset value inputs that were added to an (n, k) function to make it reversible. The constant inputs are known as ancilla inputs.

The relation between garbage outputs and constant inputs is as follows [5], [24]. # input + # constant input = # output + # garbage

#### 2.3 Reversible Gates

Several reversible gates have been proposed in the last few decades, from which the Toffoli, Peres, Feynman, and Fredkin are conventionally used to synthesize reversible circuits. Recently, researchers have proposed different gate libraries such as MCT; multiple-control Fredkin (MCF); Peres (P); NOT, CNOT, and Toffoli (NCT); multiple-control Toffoli and Peres (MCT+P); multiple-control Toffoli and multiple-control Fredkin (MCT+MCF). Among them, the MCT gate library is the most widely used for reversible logic synthesis. Thus, we use it to design a reversible circuit.

**Definition 3** A multiple-control Toffoli (MCT) gate has (k-1) control lines  $\{x_1, x_2, \ldots, x_{k-1}\}$  and one target line  $x_k$ , whose function is a mapping from  $(x_1, x_2, \ldots, x_{k-1}, x_k)$  to  $(x_1, x_2, \ldots, x_{k-1}, (x_1x_2 \cdots x_{k-1}) \oplus x_k)$ . For the case k = 1, the gate maps  $x_1$  to  $1 \oplus x_1$ .

Here, an MCT gate with (k-1) controls is denoted by Toffoli-k. Toffoli-1 and Toffoli-2 are also called NOT and Controlled-NOT (CNOT), respectively, whereas Toffoli-3 is the original Toffoli gate. The schematics of MCT gates are shown in Fig. 2.1. The control lines are denoted by black dots (•), whereas the target line is denoted by  $\bigoplus$ .

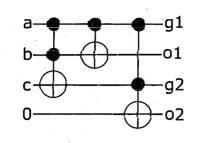

Figure 2.2: Reversible circuit.

#### 2.4 Reversible Circuits

A reversible function can be realized by cascading reversible gates where fan-out and feedback are not directly allowed in the realization of a reversible circuit. In reversible circuits, each variable of the function is represented using a circuit line. A Boolean function that is not reversible can be transformed into a reversible function by adding extra-working lines to ensure reversibility. The extra inputs in a reversible function can be preset to a constant value, which can either be 0 or 1. The extra outputs are referred to as garbage outputs. Figure 2.2 shows a reversible circuit with three reversible gates, one constant input (0), two garbage outputs ( $g_1, g_2$ ), and two outputs ( $o_1, o_2$ ). Minimum numbers of reversible gates, constant inputs, and garbage outputs are the properties of a good quality of reversible circuit. In this work, we focus on minimizing the MCT gate count in reversible circuits.

#### 2.5 Quantum Computation

The logic representation in quantum computation is quite different from that in classical computation. The basic unit of information in quantum computation is a qubit represented by a state vector. The states  $|0\rangle = \begin{pmatrix} 1 \\ 0 \end{pmatrix}$  or  $|1\rangle = \begin{pmatrix} 0 \\ 1 \end{pmatrix}$  are known as the computational basis states. The state of an arbitrary qubit  $\alpha |0\rangle + \beta |1\rangle$  is described by the vector  $\begin{pmatrix} \alpha \\ \beta \end{pmatrix}$ , where  $\alpha$  and  $\beta$  are complex numbers that satisfy the constraint  $|\alpha|^2 + |\beta|^2 = 1$ . The measurement of a qubit can either be 0 with probability  $|\alpha|^2$  or 1 with probability  $|\beta|^2$ . Similarly, a generalized 2-qubit state can be described [1] as

$$|\Psi\rangle = \lambda_1 |00\rangle + \lambda_2 |01\rangle + \lambda_3 |10\rangle + \lambda_4 |11\rangle = \begin{pmatrix} \lambda_1 \\ \lambda_2 \\ \lambda_3 \\ \lambda_4 \end{pmatrix},$$

| Gate Name                 | Gate Symbols  | Matrix                                                                                                                                                   |  |  |

|---------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NOT                       | a o1          | $\begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix}$                                                                                                           |  |  |

| CNOT                      | a01<br>b02    | $\begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \end{pmatrix}$                                                         |  |  |

| Controlled-V              | a o1<br>b o2  | $\begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & \frac{(1+i)}{2} & \frac{(1-i)}{2} \\ 0 & 0 & \frac{(1-i)}{2} & \frac{(1+i)}{2} \end{pmatrix}$ |  |  |

| Controlled- $V^{\dagger}$ | a o1<br>bt o2 | $\begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & \frac{(1-i)}{2} & \frac{(1+i)}{2} \\ 0 & 0 & \frac{(1+i)}{2} & \frac{(1-i)}{2} \end{pmatrix}$ |  |  |

Table 2.4: Quantum gate symbols and unitary matrices [1].

where  $\lambda_1 \lambda_4 = \lambda_2 \lambda_3$  for non-entanglement.

On the contrary, a classical bit has a state that can either be 0 or 1, which is analogous to the measurement of a qubit state of  $|0\rangle$  or  $|1\rangle$  respectively. The main difference between bits and qubits is that the former can be in the state 0 or 1, whereas the latter can be in a superposition of  $|0\rangle$  and  $|1\rangle$ .

#### 2.6 Quantum Gates

Quantum gates are the building blocks of quantum circuits, similar to classical logic gates, e.g., AND, OR, and NOT, being the building blocks of conventional digital circuits. Several quantum gates have been defined and studied, but we concentrate on the elementary quantum gates NOT, CNOT, Controlled-V, and Controlled-V<sup>†</sup>, which are also known as quantum primitives. This set of gates is known as the NCV gate library. These gates have been widely used in the synthesis of binary reversible functions. Elementary gates are represented by unitary matrices. A gate which acts on k qubits is represented by a  $2^k \times 2^k$  unitary matrix [22], which may include complex elements, as shown in Table 2.4.

The 2-line Controlled-V gate changes the target line using the transformation defined by the matrix  $V = \frac{1+i}{2} \begin{pmatrix} 1 & -i \\ -i & 1 \end{pmatrix}$  if the single control line has a value of 1. The 2-line Controlled-V<sup>†</sup> gate changes the target line using the transformation

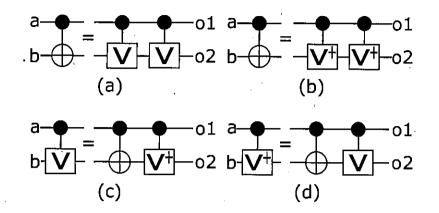

Figure 2.3: Splitting and merging rules

Figure 2.4: Deletion rule.

defined by the matrix  $V^{\dagger} = V^{-1} = \frac{1-i}{2} \begin{pmatrix} 1 & i \\ i & 1 \end{pmatrix}$  if the single control line has a value of 1. The gates V and V<sup>†</sup> are referred to as square-root-of-NOT gates because  $V^2 = (V^{\dagger})^2 = \begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix}$ .

The Controlled-V and Controlled-V<sup> $\dagger$ </sup> gates are inverses of each other, whereas NOT and CNOT (generally MCT gates) are self-inverse gates. Two adjacent Controlled-V (or Controlled-V<sup> $\dagger$ </sup>) gates with the same target and control can be replaced by a CNOT. A primitive from CNOT, Controlled-V, and Controlled-V<sup> $\dagger$ </sup> can be represented by a pair of other primitives, as shown in Fig. 2.3; this is referred to as the splitting rule. The inverse of the splitting rule is the merging rule.

If two adjacent gates form the identity function, then they can be deleted, this known as the deletion rule. Therefore, two NOT gates, two CNOT gates, and an adjacent (Controlled-V, Controlled-V<sup>†</sup>) pair (any order) with the same target and control can be eliminated, as depicted in Fig. 2.4.

The mobility of gates is determined using the following property [11], which is called the moving rule.

**Property 1** (Moving rule) Two adjacent gates  $g_1$  and  $g_2$  with controls  $c_1$  and  $c_2$ and targets  $t_1$  and  $t_2$ , respectively, can be interchanged if  $t_2 \notin c_1$  and  $t_1 \notin c_2$ .

Figure 2.5: Merged 2-qubit gate.

**Example 1** An elementary quantum gate has zero or one control and one target. Only a NOT gate has no control. In Fig. 2.7 (a), gates  $g_1$  and  $g_2$  with controls  $\{a\}$ and  $\{b\}$  and targets c and c, respectively, can be interchanged because  $c \notin \{a\}$  and  $c \notin \{b\}$ . Subsequently, gates  $g_1$  and  $g_3$  with controls  $\{a\}$  and  $\{a\}$  and targets c and b, respectively, can be interchanged because they satisfy the same condition. Thus, the gate  $g_1$  can be moved to any other location in the circuit.

The deletion and merging rules reduce the quantum gates in a circuit, whereas the moving rule enhances the applicability of the deletion and merging rules.

Hung et al. [25] showed that when both CNOT and Controlled-V (or Controlled- $V^{\dagger}$ ) are operating on the same two qubits in a symmetric pattern as shown in Fig. 2.5, their total QC is considered to be one as well. We call this the 2-qubit gate rule in the QC metrics.

The main concept of Hung et al. [25] came from the work by J. Smolin and D. DiVincenzo [26]. They considered the merged 2-qubit gate as another type of fundamental 2x2 reversible logic gate referred to as the integrated qubit gate [26]. This gate is implemented with a Feynman gate with either a Controlled-V or Controlled V+ gate. The QC of the integrated qubit gate is 1, and its worst-case delay is 1. They also presented an analytic construction of 3-bit quantum Fredkin gate that uses only five quantum gates, each acting on only two qubits. It is realized using two Feynman gates, a Controlled-V gate, and two integrated qubit gates. The quantum representation of the Fredkin gate is shown in Fig. 2.6. The second and third gates in Fig. 2.6 are each acting on the same two bits, and therefore can be replaced by a

Figure 2.6: Quantum gate representation of the Fredkin Gate.

single 2-bit gate. Similarly, the last two gates are two adjacent gates acting on the same two bits. By merging these two gates, a 5-gate design is produced.

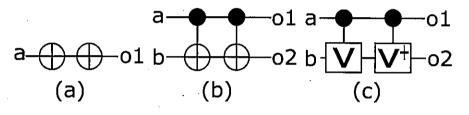

#### 2.7 Quantum Circuits

A quantum circuit is a model for quantum computation and can be realized using cascading quantum gates. Quantum operations are all reversible, and every classical reversible circuit may be implemented in quantum technology. The number of elementary quantum gates required to implement a reversible circuit is the QC of a reversible circuit. The QC is an important parameter to determine the quality of quantum and reversible circuits. Note that a reversible circuit may have multiple quantum circuit realizations.

For example, Figure 2.7 shows four realizations of the Toffoli-3 gate. Figure 2.7 (b) is the reverse representation of Figure 2.7 (a). Figures 2.7 (c) and (d) are obtained by interchanging the Controlled-V and Controlled-V<sup> $\dagger$ </sup> in Figures 2.7 (a) and (b), respectively. The QC of the circuits in Figure 2.7 is 5 as they each consists of five quantum gates.

However, during the transformation of MCT circuits into quantum circuits, the QC of MCT circuits may differ according to the selection of the quantum gate realization of Toffoli gates.

For example, consider the MCT circuit in Figure 2.2. The circuit has two Toffoli-3 gates. If the two Toffoli gates are replaced by the realization in Figure 2.7 (a), the QC of the circuit becomes 9. However, if the first Toffoli gate is replaced by the realization in Figure 2.7 (a) and if the second gate is replaced by the realization in Figure 2.7 (b), the QC becomes 8. The selection of an appropriate realization of the Toffoli gate does not affect the functionality of the circuits; however, it may provide better quality circuits in terms of the quantum gate count. This concept is used in the reduction of the QC in Chapter 6.

15

;

## Chapter 3

### Literature Review

This chapter provides previous synthesis and optimization approaches used to design the ALUs and adder/subtractor block. We know that the logic unit is a key element in programmable computing devices and an adder/subtractor block is also an important element in designing ALU. A faster adder/subtractor block will increase the efficiency of the ALUs performance and that of the whole system. Here, the objective is to design ALUs or adder/subtractor blocks that have better performance and lower power consumption than existing systems. In this chapter, we discuss several designs of ALUs and adder/subtractor blocks based on reversible logic.

#### 3.1 Related Works

Rangaraju et al. [27] proposed three designs for reversible half and full adder/subtractor circuits using a different gate library that includes Feynman [28], Fredkin, TR, and Peres gates. In some of the cases, their designs require five or more working lines, a large number of reversible gates, constant inputs, and garbage outputs with a high QC. Moghimi et al. [29] proposed a new 4x4 universal reversible gate as a cost-efficient full adder/subtractor in terms of reversible and quantum metrics. They have shown improvements over existing full adder/subtractor designs by comparing the number of reversible gates, garbage outputs, constant inputs, and the QC. Sultan et al. [30] proposed a full adder/subtractor circuit using Feynman and Peres gates, showing improvements over the previous work [27] in terms of the number of reversible gates, garbage outputs, constant inputs, and the QC. Table 3.1 shows a summary of related works on reversible adder/subtractor circuits.

Gupta et al. [33] proposed a reversible LU with eight operations using five inputs. The Mini-ALU reported in Revlib [34] can perform four operations, i.e., OR, AND,

| Reversible and quantum metrics |            |          |         |     |  |  |

|--------------------------------|------------|----------|---------|-----|--|--|

| Design                         | Reversible | Constant | Garbage | QC  |  |  |

|                                | Gates      | Inputs   | Outputs |     |  |  |

| Design 1 [27]                  |            | 3        | 5       | 21  |  |  |

| Design 2 [27]                  | 4          | 1        | 3       | 14  |  |  |

| Design 3 [27]                  | 4          | 1        | 3       | 10  |  |  |

| Design 1 [31]                  | 8          | 5        | 7       | _28 |  |  |

| Design 2 [31]                  | 10         | - 5      | . 8     | 24  |  |  |

| Design [32]                    | 3          | 2        | • 4     | 18  |  |  |

| Design [29]                    | · 1        | 0        | · 2     | 11  |  |  |

| Design [30]                    | 4          | 3        | 1       | 10  |  |  |

|                                |            |          |         |     |  |  |

Table 3.1: Comparison of existing reversible adder/subtractor circuits.

ADD, and Identity. Both ALUs were implemented using the MCT gate library. Table 3.2 shows a summary of related works on reversible ALUs.

| able 5.2: Related works on reversible AL |             |                  |     |     |  |

|------------------------------------------|-------------|------------------|-----|-----|--|

|                                          |             | Reversible Gates | QC  |     |  |

| Ì                                        | Design [33] |                  | 114 |     |  |

|                                          | Design [34] | 6                | 62  | 1.0 |  |

Table 3.2: Related works on reversible ALUs.

As seen in Figure 1.1, the design flow of reversible synthesis comprises three stages. We found that related works for reversible adder/subtractors and ALUs have limited the analysis of the level of reversible function design. Here, we investigate the function design thoroughly to improve reversible circuits. The minimization problem for MCT circuits is also extended accordingly. As a result, we obtain the minimum MCT circuits of the adder/subtractors and the ALUs. We also provide the quantum circuits of our reversible adder/subtractors. There were very few works that proposed the quantum circuit implementation for the adder/subtractors, while obtaining the quantum circuit is the goal of the reversible synthesis.

In this thesis, we adopt the MCT gate library to design reversible adder/subtractor and simple ALU circuits. As far as we know, there are no existing works on the optimization of reversible full adder/subtractor circuits using only the MCT gate library with the lowest possible number of working lines, constant inputs, and garbage outputs even though the MCT gate library is the most fundamental and widely-used gate library for the synthesis of reversible circuits.

### Chapter 4

## **Design of Reversible Functions**

In the process of reversible logic synthesis, the design of reversible functions is very important and the embedding of irreversible functions into reversible functions is required before they can be applied to existing synthesis methods. Irreversible functions can be embedded into incompletely-specified or completely specified reversible functions [23] depending on which synthesis methods used. In this chapter, we embed irreversible functions into incompletely-specified reversible functions because the synthesis method we used supports it. Note that many syntheses approaches require a completely specified function so that often all don't care must be assigned to a concrete value.

This chapter also discusses the unique and interesting method to improve reversible circuits. The whole process of reversible circuit synthesis is different from that of related works; we try improvements on the level of the functional design. Our approach to investigate the reversible functions includes the following:

- Embedding irreversible functions into incompletely-specified reversible functions

- OA,

- Permutation of the function outputs

Moreover, we provide some extensions of these techniques to deal with a set of incompletely-specified reversible functions.

#### 4.1 Embedding Irreversible Functions into Incompletely-Specified Reversible Functions

The functions of the adder/subtractor and ALU are irreversible. To obtain a reversible circuit of an irreversible function, we embed the irreversible function into an incompletely-specified function to make it reversible. Here, we set a restriction in which only the minimum necessary ancilla lines are added for embedding. Ancilla lines refer to when additional input Boolean variables are needed to construct the output function. Consider the functional specification of ALU in Table 4.1, where '-' denotes the don't-care value. We added two garbage outputs to the irreversible function to embed it into a reversible function. The garbage outputs are the columns of the don't-care values in the truth table. Therefore, this function is called an incompletely-specified reversible function. The required garbage outputs depend on the maximum number of repetition of an output pattern in the truth table. If the number of repetitions is M,  $\lceil \log_2 M \rceil$  garbage outputs are necessary [10]. In Table 4.1, the output patterns (0) and (1) are repeated four times for the input {0100, 1000, 1001, 1010} and {0101, 0110, 0111, 1011}, respectively, which is the maximum number of repetitions. When  $\lceil \log_2 4 \rceil = 2$ , two garbage outputs are added. However, no additional lines are required in this reversible circuit because the number of outputs is equal to the number of inputs.

Generally, an irreversible function can be embedded into a reversible function by adding necessary garbage outputs; the resulting reversible function is incompletely specified. To discuss incompletely-specified functions, we provide some necessary definitions. Hereafter, 'a reversible function' indicates a fully-specified reversible function unless otherwise noted.

**Definition 4** An incompletely-specified reversible function is abbreviated as ISRF. Let F be a (fully-specified) reversible function. We say that F matches an ISRF F' if  $F(\mathbf{X}) = F'(\mathbf{X})$  for all inputs  $\mathbf{X} \in \{0,1\}^n$  except when  $F'(\mathbf{X}) = \text{`-`}$ , where `-` is the don't-care value.  $F \in :F'$  denotes that F matches F'. As an extension, for a set of ISRFs  $\mathcal{F}$ ,  $F \in :\mathcal{F}$  denotes that  $F \in :F'$  holds for some ISRF F' in  $\mathcal{F}$ . We also say that F matches  $\mathcal{F}$  if  $F \in :\mathcal{F}$ .

The minimality, in this thesis, is defined by the gate count of MCT circuits. Below, an extension of the minimality to a set of ISRFs is given.

**Definition 5** Let F be a reversible function of n variables. Among all n-bit MCT circuits that realize F, those with the exact minimum number of MCT gates are called the minimum MCT circuits of F. The size of F is defined by the gate count of the minimum MCT circuit of F, which is denoted by  $\gamma(F)$ . We extend  $\gamma$  to that for a set of ISRFs  $\mathcal{F}$ ;  $\gamma(\mathcal{F})$  is defined by the minimum  $\gamma(F)$  for all  $F \in: \mathcal{F}$ , namely,  $\gamma(\mathcal{F}) = \min\{\gamma(F) \mid F \in: \mathcal{F}\}$ .  $OPT(\mathcal{F})$  is the set of reversible functions  $F \in: \mathcal{F}$  with the minimum size  $\gamma(\mathcal{F})$ ;  $OPT(\mathcal{F}) = \{F \mid F \in: \mathcal{F}, \gamma(F) = \gamma(\mathcal{F})\}$ .

| $S_1$ | $S_2$ | Α | В  | $g_1$          | $g_2$      | $O_1$ | $O_2$ |

|-------|-------|---|----|----------------|------------|-------|-------|

| 0     | 0     | 0 | 0  | -              | -          | 0     | 0     |

| 0     | 0     | 0 | 1- | -              | -          | 0     | 1     |

| 0     | 0     | 1 | 0  | -              | -          | 0     | 1     |

| 0     | 0     | 1 | 1  | -              | -          | 1     | 0     |

| 0     | 1     | 0 | 0  | -              | -          | -     | 0     |

| 0     | 1     | 0 | 1  | -              | · _        | -     | 1     |

| 0     | 1     | 1 | 0  | -              | <b>-</b> ' | -     | 1     |

| 0     | 1     | 1 | 1  | -              | -          | -     | 1     |

| 1     | · 0   | 0 | 0  | - ·            | · _        | -     | 0     |

| 1.    | 0     | 0 | 1  | . •            | r          | -     | 0     |

| 1     | 0     | 1 | 0  | -              | -          | -     | 0     |

| 1     | 0     | 1 | 1  | ÷ .            | -          | -     | 1     |

| 1     | 1     | 0 | 0  | -              | -          | 0     | 0     |

| 1     | 1     | 0 | 1  | - <sup>`</sup> | -          | 1     | 1     |

| 1     | 1     | 1 | 0  | -              |            | 0     | 1     |

| 1     | 1     | 1 | 1  | <b>-</b> '     | -          | 0     | 0     |

Table 4.1: Incompletely-specified function ALU.

#### 4.2 Operation Assignment (OA)

In this thesis, we introduce a new approach called synthesis with OA. It is a permutation of groups of rows in the truth table. This approach is applicable to circuits that have more than one operations such as adder/subtractor and ALU. This type of circuit has selector bits to choose the desired operation. Even if the set of operations is the same, the functions with those operations vary according to the assignment of the selector bits to the operations. Our approach is to try all permutations of operations and find the minimum circuit realization. If a function has m selector bits, then  $2^{m}!$  variants are considered. To utilize the concept of the permutation of operations, we give a formal definition of an equivalence relation to OA.

**Definition 6** Suppose that a multiple-output function F has m selector bits  $\{S_1, S_2, \ldots, S_m\}$  and is represented by  $F(S_1, S_2, \ldots, S_m, \mathbf{X})$ . F may be an ISRF. For a nonnegative integer i ( $0 \le i \le 2^m - 1$ ),  $F_i(\mathbf{X})$  denotes the cofactor  $F(i_1, i_2, \ldots, i_m, \mathbf{X})$ , where  $(i_1, i_2, \ldots, i_m)$  is an m-bit binary representation of i. The cofactors  $F_i(\mathbf{X})$  are called operations of  $F(S_1, S_2, \ldots, S_m, \mathbf{X})$ . The literals  $\overline{S}$  and S are denoted by  $S^0$  and  $S^1$ , respectively. By using these notations, the Shannon expansion of F with respect to variables  $S_1, S_2, \ldots, S_m$  is represented by  $F(S_1, S_2, \ldots, S_m, \mathbf{X}) = \bigvee_{0 \le i \le 2^m - 1} S_1^{i_1} S_2^{i_2} \cdots S_m^{i_m} \cdot F_n(i)(\mathbf{X})$ is OA-equivalent to  $F(S_1, S_2, \ldots, S_m, \mathbf{X})$  if  $\pi$  is a permutation of  $\{0, 1, \ldots, 2^m - 1\}$ .

| Table 4.2: Four operations of ALU.                       |                |                 |          |       |       |                 |

|----------------------------------------------------------|----------------|-----------------|----------|-------|-------|-----------------|

| 10010 1.2.                                               | $\frac{1}{A}$  | $\frac{opt}{B}$ | $g_1$    | $g_2$ | $O_1$ | $\frac{O}{O_2}$ |

| $\begin{array}{l} \text{ADD:} \\ F_0(A,B) = \end{array}$ | 0              | 0               | -        | -     | 0     | 0.              |

|                                                          | .0             | 1               | - ·      | -     | 0     | 1               |

|                                                          | 1              | 0 ′             | <u> </u> | -     | 0     | 1               |

|                                                          | 1              | 1               |          | -     | 1     | 0               |

| OR: $F_1(A, B) =$                                        | A              | B               | <u>_</u> | 00    | $O_1$ | $O_2$           |

|                                                          |                | $\frac{D}{0}$   | $g_1$    | $g_2$ | UI    |                 |

|                                                          | 0              | Ū.              | -        | · -   | -     | 0               |

|                                                          | 0              | 1               | -        | -     |       | 1               |

|                                                          | 1              | 0               | -        |       | -     | 1               |

|                                                          | 1              | 1               | -        | -     |       | 1 .             |

| AND: $F_2(A, B) =$                                       | $\overline{A}$ | B               | · ·      | ~     | 0     |                 |

|                                                          |                |                 | $g_1$    | $g_2$ | $O_1$ | $O_2$           |

|                                                          | 0              | 0               | -        | - '   | -     | 0               |

|                                                          | 0              | 1               | -        | -     | -     | 0               |

|                                                          | 1              | 0               | -        | -     | -     | 0               |

|                                                          | 1              | 1               | · _      | -     | ·     | 1               |

|                                                          | $\overline{A}$ | B               |          |       | -     |                 |

| SUB: $F_3(A, B) =$                                       |                |                 | $g_1$    | $g_2$ | $O_1$ | $O_2$           |

|                                                          | 0              | Ò               | -        | -'    | 0     | 0               |

|                                                          | 0              | 1               | -        | _     | - 1   | 1               |

|                                                          | 1              | 0               | · _      | -     | 0     | 1               |

|                                                          | 1              | 1               | -        | -     | 0     | 0               |

The set of all functions OA-equivalent to F is called the OA-equivalence class of Fand denoted by OAEC(F), in which the selector bits  $\{S_1, S_2, \ldots, S_m\}$  of F is assumed to be specified in the definition of F.

Note that m selector bits can identify up to  $2^m$  operations. Therefore, for a function with m selector bits, there exist at most  $2^m!$  OA-equivalent functions by the permutation of  $2^m$  operations.

**Property 2** For a function F with m selector bits,  $|OAEC(F)| \leq 2^{m}!$ .

For a function F and a circuit C, it is commonly said that C realizes F if the function of C is equal to F. We also extend the concept of circuit realization from a reversible function to a set of ISRFs.

**Definition 7** Let C be a reversible circuit and  $\mathcal{F}$  be a set of ISRFs. We say that C realizes  $\mathcal{F}$  if the function of C matches  $\mathcal{F}$ .

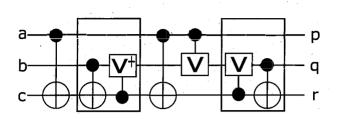

Figure 4.1: (a) Circuit realizing ALU. (b) Circuit realizing OAEC(ALU).

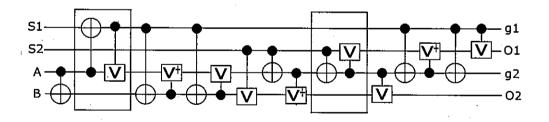

**Example 2** Consider the function of an ALU shown in Table 4.1, in which  $S_1$  and  $S_2$  are the selector bits. Table 4.2 shows the four operations  $F_0, \ldots, F_3$  of the ALU. With these operations, the ALU is represented by  $\bar{S}_1 \bar{S}_2 F_0(\mathbf{X}) \vee \bar{S}_1 S_2 F_1(\mathbf{X}) \vee S_1 \bar{S}_2 F_2(\mathbf{X}) \vee S_1 S_2 F_3(\mathbf{X})$ . For example, the function  $ALU' = \bar{S}_1 \bar{S}_2 F_1(\mathbf{X}) \vee \bar{S}_1 S_2 F_0(\mathbf{X}) \vee S_1 \bar{S}_2 F_3(\mathbf{X}) \vee S_1 S_2 F_2(\mathbf{X})$  made by a permutation of operations is OA-equivalent to ALU. The difference between ALU and ALU' is the assignment of operations, which is summarized in Table 4.3. A function that is OA-equivalent to ALU provides the same set of operations as ALU. However, the cost related to their circuit realizations are generally different. A minimum MCT circuit of ALU with the original assignment in Table 4.3 is shown in Figure 4.1 (a) using seven reversible gates (one NOT gate, two CNOT, and four Toffoli-3 gates) with a QC of 23. If we use a different assignment of operations as ALU', a different circuit realization using six gates (two CNOT and four Toffoli-3 gates) with a QC of 22 is obtained, as shown in Figure 4.1 (b). This example demonstrates that permutation of operations directly affects on the cost of reversible circuit realization.

## 4.3 Permutation of Function Outputs

The idea of permutation of outputs of a reversible function was originally introduced by Wille et al. [23], called as Synthesis with Output Permutation (SWOP). The following definition is the ISRF version of SWOP and its extension to a set of ISRFs.

Figure 4.2: Circuit realizing PEC(ALU).

**Definition 8** For a given ISRF F, the set of variants made by the permutation of outputs in F is called the P-equivalence class of F denoted by PEC(F). We extend PEC so that it accepts a set of ISRFs  $\mathcal{F}: PEC(\mathcal{F}) = \bigcup_{F \in \mathcal{F}} PEC(F)$ .

P-equivalence is a permutation of columns in the truth table, whereas OA-equivalence is a permutation of groups of rows in the truth table.

|PEC(F)| for an *n*-output ISRF F is at maximum n! because PEC(F) is a permutation of the outputs of F.

#### **Property 3** For an *n*-output ISRF F, $|PEC(F)| \le n!$ .

Note that the P-equivalence class of a reversible function F is different from the conjugacy class [35] of F (also called the line reordering). In the conjugacy class, the inputs and outputs in F are relabeled simultaneously. In the P-equivalence class, the outputs in F are relabeled, but the inputs are not altered. It is known that every function in the conjugacy class of F can be realized in a circuit with the same gate count. However, the gate count of the circuit of a function in the P-equivalence class of F is generally not the same as that of F (e.g., Example 3). This means that there may be a smaller function in the gate count than F among functions matching PEC(F).

**Example 3** Consider that the ALU shown in Table 4.1 maps the input  $(S_1, S_2, A, B)$  to the output  $(g_1, g_2, O_1, O_2)$ . The minimum MCT circuit shown in Fig. 4.1 (a) consists of seven gates. Figure 4.2 shows an MCT circuit realizing PEC(ALU), in which the four outputs of the function are reordered to another position. More precisely, the MCT circuit shown in Fig. 4.2 maps the input  $(S_1, S_2, A, B)$  to the output  $(g_1, O_1, g_2, O_2)$ . This reduces the overall number of gates from seven to six.

# Chapter 5

# Synthesis of Minimum Reversible Circuits

The two techniques, OAEC and PEC, discussed in Chapter 4 can be combined to further reduce the number of gates in a circuit. In this chapter, we discuss the minimization of MCT circuits realizing PEC(OAEC(F)) for a given F. By Definition 8, PEC is extended to accept a set of ISRFs like OAEC(F).

## 5.1 Minimization Algorithm

The adder/subtractor and ALUs proposed in this sections are 4-bit or 5-bit functions. The minimum MCT circuits for all the 4-bit reversible functions have been obtained by Golubitsky et al. [35]. Their algorithm, however, does not support ISRFs. An SAT-based algorithm [16] can be applied to ISRFs. The algorithm produces one minimum circuit for a given ISRF; however, it does not provide a list of minimum circuits for other reversible functions that match the ISRF. Thus, instead of using these sophisticated algorithms, we use the hash tables of minimum MCT circuits with up to seven gates for 4-bit functions and five gates for 5-bit functions. The tables are constructed by enumerating all possible gate combinations. The procedure MAKETABLE in Fig. 5.1 is used to construct such tables. Although the applicability of this simple strategy is limited to small circuits because of high memory consumption, it is sufficient to achieve our purpose.

In the algorithm, the number of input/output lines, or bits, are denoted as n, and minimum MCT circuits with i gates are stored in  $ht_i$ . The function FINDOPT obtains  $OPT(\mathcal{F})$  and its minimum MCT circuits in pairs by searching for  $ht_1, ht_2, \ldots$ successively. A memory saving technique with symmetry [35] is used, however, the description of this technique is omitted from Fig. 5.1. We combine the hash tables of these minimum circuits and the techniques proposed in Chapter 4, to obtain the minimum MCT realization of the adder/subtractor and ALU circuits.

We also compare the results obtained using FINDOPT with those using the SATbased algorithm. The results reveal that the list of minimum MCT circuits obtained using FINDOPT has a better circuit in terms of QC as compared to the one obtained using the SAT-based algorithm.

## 5.2 Reversible Adder/Subtractor

In this section, we obtain the minimum MCT circuits of half and full adder/subtractors using our proposed technique. An adder/subtractor has two operations, i.e., 'adder' and 'subtractor', and the 1-bit selector S decides the operations to be performed. Possible assignments of operations are shown in Table 5.1. Along with half and full adders, there are half and full adder/subtractors.

Table 5.1: OA for adder/subtractor.

| S | Assignment 1 | Assignment 2 |

|---|--------------|--------------|

| 0 | Adder        | Subtractor   |

| 1 | Subtractor   | Adder        |

#### 5.2.1 Half Adder/Subtractor

According to the OA shown in Table 5.1, two OA-equivalent functions of the half adder/subtractor exist for Assignments 1 and 2. Equations (5.1) and (5.2) provide the logical expressions of these functions. C/B' and S/D' denote Carry/Borrow and Sum/Difference, respectively.

$$\begin{cases} C/B = \bar{S}AB \lor S(AB \oplus B) \\ S/D = A \oplus B \end{cases}$$

$$\begin{cases} C/B = \bar{S}(AB \oplus B) \lor SAB \\ S/D = A \oplus B \end{cases}$$

(5.1)

$$(5.2)$$

Equation (5.1) is embedded in the truth table, as in Table 5.2, which is denoted by  $hAS_1$ . During embedding, two garbage outputs,  $g_1$  and  $g_2$ , are added because they are required by the maximum number of repetitions of an output pattern in the truth table. To balance the numbers of inputs and outputs, a constant input c = 0is added. Similarly, Equation (5.2) is embedded in the truth table as in Table 5.3, which is denoted by  $hAS_2$ .

```

1: var ht_0, ht_1, ht_2, \ldots: Hash Table;

2: procedure MAKETABLE(m)

\triangleright Input: m is an integer.

3:

\triangleright Side Effect: minimum MCT circuits with up to m gates are stored in the

4:

hash tables ht_0, ht_1, ht_2, \ldots

if m = 0 then ht_0[identity] \leftarrow the empty circuit;

5:

6:

else

MAKETABLE(m-1);

7:

for all entry C \in ht_{m-1} do

8:

for all G \in \mathcal{G}_n do

9:

if ht_m[func(C \mid G)] = \emptyset then

10:

ht_m[func(C \mid G)] \leftarrow C \mid G;

11:

end if

12:

end for

13:

end for

14:

end if

15:

16: end procedure

17: function FINDOPT(\mathcal{F})

\triangleright Input: \mathcal{F} is a set of ISRFs.

18:

\triangleright Output: OPT(\mathcal{F}) and its minimum MCT circuits in pairs.

19:

20:

var i \leftarrow 1 : Integer;

var S \leftarrow \emptyset : Set;

21:

while (S = \emptyset) or (ht_i \text{ is not empty}) do

22:

for all key F \in ht_i do

23:

if F \in \mathcal{F} then S \leftarrow \{(F, ht_i[F])\} \cup S;

24:

25:

end if

end for

26:

27:

i \leftarrow i + 1;

end while

28:

29:

J

return S;

30: end function

```

$\mathcal{G}_n$ : set of all MCT gates with up to *n* bits.

$C \mid G$ : concatenation of circuit C and gate G.

$func(C \mid G)$ : reversible function of the circuit  $C \mid G$ .

Figure 5.1: Simple minimization algorithm with up to m gates

| С     | $S_{\cdot}$ | Α | В     | $g_1$ | $g_2$            | C/B           | S/D        |

|-------|-------------|---|-------|-------|------------------|---------------|------------|

| 0     | 0           | 0 | 0     | -     | · -              | 0             | . 0        |

| . 0   | 0           | 0 | 1     | - "   | · _              | 0             | 1          |

| 0     | 0           | 1 | 0     | · _   | -                | - 0           | 1          |

| · 0 · | 0           | 1 | 1     |       |                  | 1             | 0          |

| 0     | 1           | 0 | 0     |       | . <del>.</del> . | 0             | 0 .        |

| 0     | 1           | 0 | 1     | -     | _                | 1             | 1          |

| 0     | 1           | 1 | 0     | . –   |                  | 0             | 1          |

| 0     | 1           | 1 | 1     | -     | · ' <b>-</b>     | 0             | 0          |

| 1     | 0           | 0 | 0     | -     | <b>-</b> .       | · -           | · <u>-</u> |

| 1     | 0           | 0 | 1     | · –   | -                | -             | . –        |

| 1     | 0 .         | 1 | 0     | -     | -                |               | <u> </u>   |

| 1     | 0           | 1 | 1     | -     | · -              |               | -          |

| 1     | 1           | 0 | 0     | -     | -                | _             | · ·        |

| 1     | 1           | 0 | 1     | -     |                  | ۰ <del></del> | -          |

| 1     | 1           | 1 | . 0 ' | -     | _                |               | _ ·        |

| 1     | 1           | 1 | ·1    | -     | -                | -             |            |

Table 5.2: Incompletely specified half adder/subtractor function  $hAS_1$ .

Table 5.3: Incompletely specified half adder/subtractor function  $hAS_2$ .

| upr | every | spo | SCIIIC | u na  | anac  | iuer/su |     |

|-----|-------|-----|--------|-------|-------|---------|-----|

| C   | S     | Α   | B      | $g_1$ | $g_2$ | C/B     | S/D |

| . 0 | 0.    | 0   | 0      |       | • • • | 0       | 0   |

| 0   | 0     | 0   | 1      |       | -     | 1       | 1   |

| 0   | 0     | 1   | 0      | -     | - '   | 0       | 1   |

| 0   | 0     | 1   | 1      | -     | . –   | 0       | 0   |

| 0   | 1     | 0   | 0      | -     | -     | 0       | 0   |

| 0   | 1     | 0   | 1      | -     | -     | 0       | 1   |

| 0   | 1     | 1   | 0      | · _ · |       | 0       | 1   |

| 0   | 1     | 1   | 1      | -     | -, ,  | 1       | 0   |

| 1   | 0     | 0   | 0      | ·     | · _ ` | -       | -   |

| 1   | 0     | 0   | 1      | · _   | -,    | -       | -   |

| 1   | 0     | 1   | 0      | - ,   | -     |         | -   |

| 1   | 0.    | 1   | 1      | -     |       |         | -   |

| 1   | 1     | 0   | 0      | -     | -     | -       |     |

| 1   | 1     | 0   | 1      | -     | · _ ` | -       | -   |

| 1   | 1     | 1   | 0      | -     |       | · -     | -   |

| 1   | 1     | 1   | 1      | -     | · -,  | . –     | -   |

28

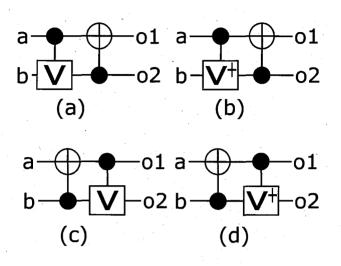

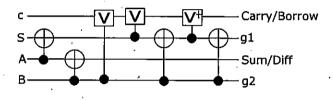

Table 5.4 shows the minimum MCT realization of the P-equivalence class of  $hAS_1$ , or  $OPT(PEC(hAS_1))$ , obtained by our FINDOPT program. The six reversible functions have minimum MCT circuits with three gates. On the right-hand side of Table 5.4, a circuit is represented by a sequence of reversible gates, in which  $(x \ y)$  represents a CNOT gate and  $(x \ y \ z)$  represents a Toffoli gate. The last parameter is the target line, and the remaining parameters are the control lines. For example, "(2 1) (3 2) (1 3 0)" in the first row represents the MCT circuit of Fig. 5.2, where the numbering of the lines is (c, S, A, B) = (0, 1, 2, 3).

| Table 5.4: $OPT(PEC(hAS_1))$ and its                     | minimum MCT circuits           |

|----------------------------------------------------------|--------------------------------|

|                                                          | Minimum MCT Circuit            |

| $(0\ 3\ 6\ 13\ 4\ 15\ 2\ 1\ 8\ 11\ 14\ 5\ 12\ 7\ 10\ 9)$ | $(2\ 1)\ (3\ 2)\ (1\ 3\ 0)$    |

| $(0\ 3\ 2\ 13\ 4\ 15\ 6\ 1\ 8\ 11\ 10\ 5\ 12\ 7\ 14\ 9)$ | $(2\ 3\ 1)\ (3\ 2)\ (1\ 3\ 0)$ |

| $(0\ 3\ 2\ 9\ 4\ 15\ 6\ 5\ 8\ 11\ 10\ 1\ 12\ 7\ 14\ 13)$ |                                |

| $(0\ 1\ 7\ 14\ 4\ 13\ 3\ 2\ 8\ 9\ 15\ 6\ 12\ 5\ 11\ 10)$ |                                |

| $(0\ 1\ 3\ 14\ 4\ 13\ 7\ 2\ 8\ 9\ 11\ 6\ 12\ 5\ 15\ 10)$ | $(2\ 3\ 1)\ (1\ 3\ 0)\ (2\ 3)$ |

| $(0\ 1\ 3\ 10\ 4\ 13\ 7\ 6\ 8\ 9\ 11\ 2\ 12\ 5\ 15\ 14)$ |                                |

Figure 5.2: Proposed reversible half adder/subtractor circuit with MCT gates.

| Table 5.5: $OPT(PEC(hAS_2))$ and its    | minimum MCT circuits           |  |  |  |  |  |  |  |

|-----------------------------------------|--------------------------------|--|--|--|--|--|--|--|

| Reversible Function Minimum MCT Circuit |                                |  |  |  |  |  |  |  |

| (0 15 6 1 4 3 2 13 8 7 14 9 12 11 10 5) | $(3\ 2)\ (2\ 1)\ (1\ 3\ 0)$    |  |  |  |  |  |  |  |

|                                         | $(1\ 3\ 0)\ (3\ 2)\ (2\ 3\ 0)$ |  |  |  |  |  |  |  |

| (0 15 2 1 4 3 6 13 8 7 10 9 12 11 14 5) | $(3\ 2)\ (2\ 3\ 1)\ (1\ 3\ 0)$ |  |  |  |  |  |  |  |

Similar experiments are conducted for  $hAS_2$ . The results, however, are not better than those for  $hAS_1$ . The  $OPT(PEC(hAS_2))$  are shown in Table 5.5. Three functions have minimum MCT circuits with three gates.

Since the possible OAs for the half adder/subtractor are  $hAS_1$  and  $hAS_2$ , we have  $OAEC(hAS_1) = \{hAS_1, hAS_2\}$ . Based on the experiments performed using  $hAS_1$  and  $hAS_2$ , we have confirmed that their minimum size is  $\gamma(PEC(OAEC(hAS_1))) =$

$\gamma(PEC(hAS_1)) = \gamma(PEC(hAS_2)) = 3$ ; additionally,  $hAS_1$  and  $hAS_2$  can be realized by MCT circuits using two CNOT gates and one Toffoli gate.

#### 5.2.2 Full Adder/Subtractor

A full adder/subtractor acts as a full adder or a full subtractor depending on the value of the selector bit S. As seen in Table 5.1, two full adder/subtractor functions are possible, whose logic expressions can be represented using Equations (5.3) and (5.4), respectively.

$$\begin{cases} C/B = \bar{S}(AB \lor AC \lor BC) \lor S(\bar{A}B \lor BC \lor \bar{A}C) \\ S/D = A \oplus B \oplus C \end{cases}$$

$$\begin{cases} C/B = \bar{S}(\bar{A}B \lor BC \lor \bar{A}C) \lor S(AB \lor AC \lor BC) \\ S/D = A \oplus B \oplus C \end{cases}$$

(5.4)

Table 5.6: Incompletely specified full adder/subtractor function  $fAS_1$ .

|        | - |     | <i>J</i> |   |                |                  | /   |     |

|--------|---|-----|----------|---|----------------|------------------|-----|-----|

|        | С | S   | A        | B | $g_1$          | $g_2$            | C/B | S/D |

|        | 0 | 0   | 0        | 0 | -              |                  | 0   | 0   |

|        | 0 | 0   | 0        | 1 |                | -                | 0   | 1   |

| •••••• | 0 | 0   | 1        | 0 |                | -                | 0   | 1   |

|        | 0 | · 0 | 1        | 1 | -              | -                | 1   | 0   |

|        | 0 | 1   | 0        | 0 | · _            | -                | 0   | , 1 |

|        | 0 | 1   | 0        | 1 | - <sup>.</sup> |                  | 1   | 0   |

|        | 0 | 1   | 1        | 0 | - '            | -                | 1   | . 0 |

|        | 0 | 1   | 1        | 1 | · <u>-</u> · · | - <b>-</b>       | 1   | . 1 |

|        | 1 | 0   | 0        | 0 | . –            | -                | 0   | 0   |

|        | 1 | 0   | 0        | 1 | -              | -                | 1   | 1   |

|        | 1 | 0   | 1        | 0 | -              | . <del>-</del> - | 1   | 1   |

|        | 1 | 0   | 1        | 1 | -              | -                | 1   | 0   |

|        | 1 | 1   | 0        | 0 | -              | <b>-</b> '       | 0   | 1   |

|        | 1 | 1   | 0 .      | 1 | -              | -                | 0   | 0   |

|        | 1 | 1   | 1        | 0 | · - ·          | -                | 0   | 0   |

|        | 1 | 1   | 1        | 1 | -              | · _              | · 1 | 1   |

|        |   |     |          |   |                |                  |     |     |

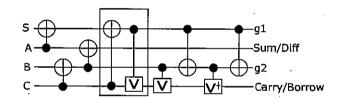

Similarly to half adder/subtractor, Equations (5.3) and (5.4) are embedded in the truth table, as in Tables 5.6 and 5.7, denoted by  $fAS_1$  and  $fAS_2$ , respectively. To balance the number of inputs and outputs, two garbage outputs,  $g_1$  and  $g_2$ , are added, but no additional lines are added.  $fAS_1$  and  $fAS_2$  can be realized in 4-line MCT circuits.

| -mpi        | inprovery specifica fair dader/substacted |      |             |                         |       |     |     |  |  |  |

|-------------|-------------------------------------------|------|-------------|-------------------------|-------|-----|-----|--|--|--|

| c           | S                                         | A    | В           | $g_1$                   | $g_2$ | C/B | S/D |  |  |  |

| 0           | 0                                         | 0    | 0           | -                       | · -   | 0   | 0   |  |  |  |

| . 0 .       | 0                                         | 0    | 1           | -                       | -     | 1 . | 1   |  |  |  |

| 0           | 0                                         | 1    | 0           | - 1                     | -     | 1 . | 1   |  |  |  |

| 0,          | 0                                         | 1    | 1           | -                       | -     | 1   | 0   |  |  |  |

| . 0         | 1                                         | 0    | 0           | – <sup>•</sup> .        |       | 0   | 1   |  |  |  |